コンピュータ・アーキテクチャ

コンピュータ・アーキテクチャ(英: computer architecture)は、基本的には、コンピュータ(特にハードウェア)の論理的な構成(法)のことである。構成要素[注釈 1]として何があるか、各構成要素がどのような機能・役割を与えられ、相互にどのような連絡をして、全体として機能しているか、に関する記述やとり決めのことである。[1] 他の語と組み合わせる場合は通常「方式」と訳す。

概説

[編集]アーキテクチャは、建築関連用語で「設計」や「様式」という意味であったのが転じて、コンピュータ分野で使われるようになった。「設計思想」などと意訳されることもある[2][3][4]。技術者や研究者の用語としては(企業ごとの用語の違いにもよるが)「方式」という語が使われることもある。

1964年のSystem/360で最初に使われた用語で、その際の意味としては、入出力インタフェースを含むコンピュータシステムのハードウェア全体(周辺機器は含まない)の、ユーザー(プログラマ、オペレーティングシステム (OS) を設計するプログラマも含む)から見た構成要素とそのインタフェースの定義であり、具体的には使用できるレジスタの構成、命令セット、入出力(チャネルコントロールワード)などである。各構成要素の実装(つまり各構成要素が具体的にどのような電子部品の組み合わせや集積回路で実現されるか)に関する記述・とりきめは含まない。つまりここでアーキテクチャはソフトウェア側から見たコンピュータの構成要素とその動作の外形的な定義であるので、アーキテクチャが同一・一定であれば、ソフトウェアの互換性が原則として保証されることになり、同一のソフトウェアを使い続けつつ上位互換のアーキテクチャを持つコンピュータへ移行することや、上位互換の周辺機器へ変更することも可能となる。また定義されたアーキテクチャを守り各構成要素の外形的な動作を記述どおりに実現しさえすれば、その内部設計や実装は技術の進歩などに応じて自由に変更・更新できる、ということになった。この結果、コンピュータ・ファミリー(シリーズ)が形成可能となった。

また、エンタープライズアーキテクチャ、ソフトウェアアーキテクチャなどの用語も増えている。

分類

[編集]この分野で評価の高いヘネシーとパターソンの2003年の書では、コンピュータ・アーキテクチャは少なくとも次の3つに分類される、とされた[5]。

- 命令セットアーキテクチャ(Instruction Set Architecture, ISA)

- 機械語またはアセンブリ言語のプログラマ(OSのプログラマも含む)から見た、CPU(プロセッサ)の抽象化されたモデル(イメージ)である[6]。ソフトウェア側から見たCPUのインタフェース定義であり、ソフトウェアがCPUに何をさせることができるか、またそれがどのようになされるか、を明らかにするものである[6]。命令セット、アドレッシングモード、レジスタ、アドレスとデータの形式などが含まれる。

- マイクロアーキテクチャ

- ISAより下層の、より具体的なシステムに関する記述であり、ISAを実装するためにシステムの構成部品をどのように接続し、それらがどのように相互にやりとりするかを示す[7]。CPUの回路的な構造[8]、とも言える。マイクロアーキテクチャにはパイプラインの長さやレイアウト、(CPU内の)キャッシュの数や容量、CPI(1命令あたりのクロックサイクル数) などが含まれる[9]。マイクロアーキテクチャは通常ISAとは何の関係も無く、それより下層に存在し、プログラマからは "見えない存在" だが、CPUの処理速度と密接な関係がある。

- システムアーキテクチャ(「システム設計」とも)

- 上述したもの以外の、コンピュータシステムのハードウェア全般に関するもの。以下のようなものが含まれる。

- バスやクロスバースイッチなどのシステムのインターコネクト

- メモリコントローラやメモリ階層

- ダイレクト・メモリー・アクセス(DMA)などのCPUオフロード機構

- マルチプロセッシングに関わる部分

- 複数のコンピュータによるシステム構成に関するもの(コンピュータ・クラスターやNUMAアーキテクチャなど)

前者2つはプロセッサのアーキテクチャである。3番目のシステムアーキテクチャは、プロセッサ以外の要素も含めコンピュータ全体のアーキテクチャである。

なお、もともとのSystem/360の「厳密に定義された」アーキテクチャには、ISAが含まれマイクロアーキテクチャが含まれず、3番目のシステムアーキテクチャのいくつかに相当するものが含まれるという相違点があるが、これは、System/360のようにまだ集積回路すら使わず単体のトランジスタやダイオードや抵抗を基板上で組み合わせて[注釈 2]実装していた当時の大型コンピュータと現在のマイクロプロセッサベースのコンピュータとでは、実装技術が大きく異なり、またビジネスモデルが変化し(周辺機器を含む)コンピュータシステム全体のレイヤの分けかたも変化したことによる。

CPUのアーキテクチャ

[編集]CPUのアーキテクチャについて説明する。

フォン・ノイマン型アーキテクチャとハーバード・アーキテクチャ

[編集]- フォン・ノイマン型アーキテクチャ

フォン・ノイマン型アーキテクチャは(ハーバード・アーキテクチャと対比される場合)、メモリ内の命令とデータは区別しない方式のことで、ひとつのメモリの中に命令とデータが置かれるアーキテクチャ。命令をデータとして扱うこともでき、データを命令として扱うこともできる。動作中に命令を書き換えることもできる。 最初、1944年にジョン・モークリーとジョン・プレスパー・エッカートがEDVACのためにつくったアーキテクチャであり、後からチームに合流したフォン・ノイマンがそれを自分の名で報告書にまとめたのでフォン・ノイマンの名で呼ばれている。

なおフォン・ノイマン型アーキテクチャだと、CPUのクロック周波数が高くなり命令フェッチや命令実行が速くなると、CPUとメモリ間のデータの移動の頻度が高くなり、命令とデータで「アクセス競合」が起き、メモリから命令やデータが到着するのを待つ状態が増え、動作が遅くなってしまう「フォン・ノイマン・ボトルネック」と呼ばれる現象が発生する。

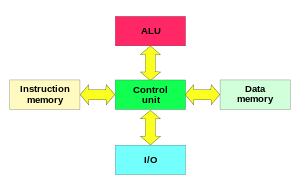

- ハーバード・アーキテクチャ

ハーバード・アーキテクチャ(Harvard Architecture)は、命令メモリとデータメモリを分離し別々に置くアーキテクチャ。メモリでの命令とデータのアクセス競合は発生せず、フォン・ノイマン・ボトルネックが解消する。ただしデータを命令として実行することはできず、動作中に命令を書き換えることもできない。1944年にIBMがハーバード大学に納入したHarvard Mark Iで最初に採用されたアーキテクチャである。

- 修正ハーバード・アーキテクチャ(en:Modified Harvard Architecture)

ハーバード・アーキテクチャを一部修正したアーキテクチャで、基本的には命令とデータを別に置いていてボトルネックが解消しており、なおかつ命令用メモリからデータ用メモリへの移動や、データ用メモリから命令用メモリへの移動も可能な方式。ハーバード・アーキテクチャを一部、修正・改良したので「修正ハーバード・アーキテクチャ」という。マイクロコントローラで主流のアーキテクチャで、基本的には命令用のフラッシュメモリとデータ用のRAMを区別しているが、命令用フラッシュメモリからデータ用のRAMにロードできたり、RAMに置いた命令を取り出しフラッシュメモリに移動し実行することもできる。現在、マイクロコントローラ以外の多くのコンピュータもこの方式を採用している。

アキュムレータ方式と汎用レジスタ方式

[編集]CPUのレジスタと演算装置(ALU)の関係性に関するアーキテクチャとしては、典型的なものとしては、アキュムレータ方式と汎用レジスタ方式がある。1970年代や1980年代のCPUや現在のマイクロコントローラの一部はアキュムレータ方式を採用しているが、これは少数派であり、現在のパーソナルコンピュータやスマートフォンなどのCPUは基本的に汎用レジスタ方式であり、こちらが現在の主流派である。

- アキュムレータ方式

演算装置で演算した結果を、必ず「アキュムレータ(accumulator、集積装置)」と呼ばれる特別な位置づけのレジスタに送り込む方式。そしてアキュムレータの値は、次の演算でオペランド(被演算子)として使われる。

1970年代や80年代など、CPUに入れられるトランジスタの数がまだかなり限られていた時代に、CPUを簡素な構造にしてトランジスタ数を減らすために考案された方式。

CPU内部では数を次々と足して総和を求める作業は頻繁に行われているが、アキュムレータ方式だと、オペランドの片方だけを次々と指定しては演算器で加算してゆくだけで総和を求めることができる。たとえばIntel 8080の「Aレジスタ」はアキュムレータである[10]。

現在では、1970年代や80年代のようにCPUに収容できるトランジスタ数が限られることは無いが、現在でもマイクロコントローラの一部ではあえてアキュムレータ方式を採用してさらに(上の節で説明した、命令用メモリとデータ用メモリを別に置く)ハーバード・アーキテクチャと組み合わせることで、簡素でコストを抑えていながら高性能のマイクロコントローラを提供しているメーカーもある[11]。

- 汎用レジスタ方式

(上で説明したアキュムレータという特別な扱いのレジスタは置かず)複数のレジスタの中から2つのレジスタを指定して、その2つの値をオペランドとして演算が可能な方式。汎用レジスタ方式だと、オペランドの組み合わせの自由度が高く、高速演算が可能になる。また、マイクロコントローラのプログラミングの際にはCコンパイラのIDE(統合開発環境)との親和性も高く、たとえばプログラムのローカル変数をマイクロコントローラの複数のレジスタに割り当てることができる。(アキュムレータ方式では割り当てられずRAMなどのメモリに割り当てなければならないのに比べて有利。)[11] 現在の技術ではCPUにトランジスタを大量に詰め込むことも容易なので、通常はこの汎用レジスタ方式を採用する。

コンピュータ全体のアーキテクチャ

[編集]プロセッサだけではなく、コンピュータシステム全体の設計とアーキテクチャについて述べる。

コンピュータの設計をする際は、まず用途や制約条件を考慮し、要素の優先順位を決定する。コンピュータ・アーキテクチャは一般に、標準規格、機能、メモリ容量、レイテンシ、スループット、消費電力、生産コストや生産性などを考慮して決められるが、また信頼性、拡張性、大きさ、重さといった要素も考慮される。それらの要素のいくつかは互いにトレードオフの関係にあり、何かを優先すると何かが犠牲になる。少数の要素を最高の状態にすることを重要視して他の要素を大きく犠牲にすることもいとわない設計法と、多くの要素をほどほどの状態に保つ設計法がある。古典的な手法としては、データの処理能力を上げることを最優先し、何がボトルネックとなり最もデータ処理能力を悪化させているかを見極め、そのボトルネックを解消するというものがあった。近年のモバイルコンピュータでは、消費電力を抑えることを優先し、何が電力を消費し電力効率を下げているのか見極め、それを取り除く工夫を重ねる。

現実のコンピュータの設計には、純粋に技術的な観点だけでなく、当該開発プロジェクトのマネージャーの個人的意向や志向も影響し、またコンピュータの開発というのは企業でビジネス(商業活動)の一部として行われているので、コンピュータ市場にすでに存在している他社のコンピュータとの競合関係や棲み分けやポジショニングといった、経営者が判断するマーケティング戦略的なことも、影響を及ぼず。

コスト

[編集]一般に、設計前に、システム要件やコンピュータ市場の状況(他社の競合製品の存在状況やその価格など)を考慮して、販売される台数(ロット)も予想しそれも織り込みつつ、製造コストの目標値が設定される。

処理能力

[編集]コンピュータの処理能力(性能)を高める手法や、その測定法や指標はいくつもある。

パーソナルコンピュータでよく使われた手法はクロック周波数を上げることで、現在でもコンピュータ商品の仕様書(スペックシート)に「○○GHz」(かつては「○○MHz」)などと表示されているものであり、CPUのクロックが一秒間に何サイクルであるかを示したものである。しかしクロック周波数で単純に処理能力の高さを測れるかというと、必ずしもそうではない。最近のCPUはスーパースケーラ方式で1クロックサイクルで複数の命令を実行することでデータ処理能力を改善しているので、それも考慮する必要がある。また2006年1月にインテルがIntel Coreシリーズの最初のものをリリースして以降は、マルチコア化つまりひとつのプロセッサに《CPUコア》を複数持たせて処理能力を高めている製品は主流であり、コア数も指標となる。喩えるなら、クロック周波数を道路の最高速度(法定速度)のようなものだとすると、コア数は道路の車線の数に相当し、最高速度が同じでも車線数が2倍、4倍、6倍になると、単位時間あたりに通る自動車の数も2倍、4倍、6倍に増えるのと同じようなもので、クロック周波数が同じでもコア数が多ければデータ処理能力は高い。(なおクロック周波数のほうは、1990年代は右肩上がりの状態であったが、2020年代にはすでに頭打ちになっている。)

他にCPUのキャッシュメモリの容量、実行ユニットの個数を増やす方法もあり、他にもバスの速度、プログラムとして実行しようとする命令の種類と順序なども処理能力に影響し、メインメモリの容量も影響する。

特に高速に大量の計算をすることを目的としたスーパーコンピュータでは「ノード」と呼ばれる同一ユニットを非常に多数並べるアーキテクチャ(並列アーキテクチャ)を採用している[12](近年のスパコンでは、数千個から数万個ほどもノードを並べる)。スーパーコンピュータの処理能力の高さは、FLOPS(フロップス)という指標で表示する方法があり、そのほかにも処理能力の高さはランキングという手法で比較することが世界的に一般的である[13]。

制御用のコンピュータでは、「速さ」を考える際に、レイテンシとスループットが重要である。レイテンシとは、ある処理が開始してから完了するまでの時間である。スループットは単位時間当たりに処理できる仕事の量である。割り込みレイテンシとは、ハードウェアのイベント(例えば、ディスクドライブの読み書きの完了)通知(割り込み)に対して、システムが応答するのにかかる時間である。性能は設計上の様々な選択によって影響される。例えば、キャッシュメモリを追加するとレイテンシは悪化するが、スループットは向上する。制御用のコンピュータでは、割り込みレイテンシの短縮が求められる。そのようなコンピュータはリアルタイム環境で運用され、所定の時間以内に処理が行われないと問題が発生する。例えばコンピュータ制御のアンチロックブレーキは、ブレーキが踏まれたら即座に制動をかけ始めなければならない。 コンピュータの性能の測定法や指標は他にもある。システムは用途によってボトルネックとなる部分が異なり、CPUバウンド(例えば数値計算など)、I/Oバウンド(Webサーバなど)、メモリバウンド(ビデオ編集など)に分けられる。サーバや携帯機器では電力消費量も重要な指標である(次の節で説明)。

ベンチマークは、一連の評価プログラムを実行し、それにかかる時間を計ることで、上述の多くの観点を考慮した性能を測定するものである。しかし、ベンチマークにも不完全性や恣意性がつきまとう。ベンチマークが異なれば、性能値が異なって示される。例えば、あるアプリケーションは高速に実行できても、別のアプリケーションでは遅いかもしれない。(おまけに、システム設計段階で、特定のベンチマークの結果向上のためにハードウェアやソフトウェアにそのベンチマークだけを高速化できる機能を(こっそりと)加えるメーカーがある。だがこの機能はそのベンチマークと類似のアプリケーションでは役に立たないことが多いので、ベンチマークの数値を鵜呑みにするわけにはいかなくなる。)

消費電力

[編集]電力効率が良く、低消費電力(消費電力が小さいこと)は、特にコンピュータが持ち運ばれるようになってからはコンピュータ設計する上で重要度が増してきた。またプロセッサの単位面積当たりのトランジスタ数が増えるに従い、電力効率が重要な観点となってきた。以前は、電力消費量を抑えると、性能が低下したりコストが増大してしまうことが起きた。ARMアーキテクチャは、処理性能を十分に保ったまま低消費電力を実現し、スマートフォンやタブレットなどモバイルコンピューティング用途(モバイル機器)では標準的な存在となった。また、組み込みシステム用プロセッサでは、(組み込み対象となる機器にもよるが)消費する電力が小さいことが至上命題だが、性能はほどほどでよい、というものも多いので、消費電力の低減を最優先してあえて処理性能を抑える設計を行う場合もある。

歴史

[編集]- 用語史

コンピュータ関連での「アーキテクチャ」という用語の使用は、1959年、IBMの研究所に所属していたライル・R・ジョンソン[注釈 4]とフレデリック・ブルックスまで遡る。ジョンソンはStretchことIBM 7030について、研究報告を書いた。彼は、コンピュータについて詳細を省いてある水準の記述をしたものを、それまで使われていた「マシン構成」[注釈 5]ではなく「システムアーキテクチャ」[注釈 6]と称した。その後、Stretchの設計者の1人である ブルックスが、ある本[14]で、「コンピュータ・アーキテクチャは他のアーキテクチャと同様、構造の利用者のニーズを決定する技法であり、それらニーズに合った経済的にも技術的にも可能な限り最適な設計を行うことである」と書いている。ブルックスは System/360 の開発でも大きな役割を果たし、そこで「アーキテクチャ」という用語は「ユーザーが知る必要のある詳細」という定義になっていった。その後、コンピュータ業界で「アーキテクチャ」という用語が様々に使われるようになった。

論文で初めて「アーキテクチャ」という用語が使われたのは、1964年の IBM System/360 に関するものであった[15]。この論文ではアーキテクチャを「プログラマから見えるシステムの属性群。すなわち、概念的構造と機能的挙動であり、データフローや制御の構成、論理設計や物理的実装とは異なる」と定義した。この定義において、「プログラマ」から見たコンピュータの機能的挙動が鍵となっている。アーキテクチャに含まれる概念的構造は機能的挙動を理解するための補助的なものであり、ユースケースの範囲を拡大可能にする。

プロセッサ内部の処理方法やメモリアクセス方法(マイクロアーキテクチャ)がコンピュータ・アーキテクチャとされるようになったのは、もっと後のことである。

各部分要素のアーキテクチャ

[編集]- 命令セットアーキテクチャ

RISC、CISC、VLIW、EPICアーキテクチャ- (実装例)x86(IA-32)、PowerPC、SPARCなど。

- マイクロアーキテクチャ

- 演算アーキテクチャ

浮動小数点、演算装置、SIMD/MIMD、ベクトル演算ユニット(ベクトル計算機) - CPU制御アーキテクチャ

ワイヤードロジック、マイクロプログラム(マイクロアーキテクチャ)、実行ユニット、制御装置 - CPU高速化アーキテクチャ

パイプライン、スーパースケーラ、アウト・オブ・オーダー実行、分岐予測、レジスタ・ウィンドウ、レジスタ・リネーミング、投機的実行 - CPUバスアーキテクチャ

CPUバス(CPU内部バス、CPU外部バス《ピン》アーキテクチャ)、バス (コンピュータ)の項を参照。<スタブ> - マルチプロセッサアーキテクチャ

対称型マルチプロセッサ(SMP)、NUMA(ASMP)、クロスバースイッチ <スタブ> - マルチスレッドアーキテクチャ

ブロック型マルチスレッディング、インターリーブ型マルチスレッディング、同時マルチスレッディング

- 演算アーキテクチャ

- システムアーキテクチャ

- 制御アーキテクチャ

割り込み制御、入出力制御 - バスアーキテクチャ

ハーバードアーキテクチャ、プログラム内蔵方式(ノイマン型を含む)

クロスバースイッチ

システムバス、メモリバス、入出力バス。

バス (コンピュータ)の項を参照。<スタブ>- (実装例)ISA、PCI等の拡張バスアーキテクチャ。

- メモリアーキテクチャ

キャッシュメモリ、仮想記憶、TLB <スタブ> -- メモリ - ネットワークアーキテクチャ

<スタブ> -- コンピュータネットワーク - オペレーティングシステムアーキテクチャ

ページング方式アーキテクチャ。<スタブ> - 分散処理アーキテクチャー

- 制御アーキテクチャ

注釈

[編集]- ^ 英語では通常、コンポーネント componentと言う。

- ^ 《単体》は英語でディスクリート(discrete)と言い、トランジスタやダイオードや抵抗など単体の半導体部品を、集積回路と区別して、ディスクリート部品と言い、単体部品を基板で組み合わせて作る回路をディスクリート回路と言う。

- ^ 補足情報。アーキテクチャの話ではなく、話がかなりそれてしまうが、プロセッサやCPUのアーキテクチャが決定した後の、設計工程について。

CPU設計では、ISAとマイクロアーキテクチャが決定されると、実際のハードウェアが設計される。この設計工程を一般に「実装」と呼ぶ。実装はアーキテクチャ定義には通常含まれず、ハードウェア設計に含まれる。

実装はさらに以下の3段階に分けられる。

- 論理実装/設計 - マイクロアーキテクチャで定義されたブロックを論理式あるいは論理ゲートレベルの回路で表す。

- 回路実装/設計 - マイクロアーキテクチャ上のブロック(あるいはそれと等価な論理式)やその論理回路をトランジスタレベルのデジタル回路で表す。

- 物理実装/設計 - 回路図に従い、チップ上の部品配置や基板上の部品配置、基板間の接続ルートなどを設計する。

- ^ 英: Lyle R. Johnson

- ^ 英: machine organization

- ^ 英: system architecture

出典

[編集]- ^ [1]

- ^ 橋本昌嗣『コンピュータは私たちをどう進化させるのか: 必要な情報技術がわかる8つの授業』株式会社ポプラ社、2016年12月8日、7頁。ISBN 978-4-591-15285-0。

- ^ 玉田俊平太『日本のイノベーションのジレンマ 第2版 破壊的イノベーターになるための7つのステップ』翔泳社、2020年8月25日、67頁。ISBN 978-4-7981-6638-4。

- ^ 最上千佳子『ITIL 4の教本 ベストプラクティスで学ぶサービスマネジメントの教科書』翔泳社、2022年3月16日、226頁。ISBN 978-4-7981-7421-1。

- ^ John L. Hennessy and David A. Patterson (2003年). Computer Architecture: A Quantitative Approach (Third Edition ed.). Morgan Kaufmann Publishers, Inc. ISBN 1558605967

- ^ a b Arm, What is ISA?

- ^ Phillip A. Laplante (2001年). Dictionary of Computer Science, Engineering, and Technology. CRC Press. pp. 94–95. ISBN 0849326915

- ^ ZDNET

- ^ ARM, Architecture and micro-architecture

- ^ 小松「Intel 8080」

- ^ a b 菅井賢、STマイクロエレクトロニクス「マイコンのアーキテクチャって何?」

- ^ 理化学研究所、ソフトウェア技術チーム「スーパーコンピュータとアプリケーションの性能

- ^ [2]

- ^ Planning a Computer System: Project Stretch、1962年

- ^ G. M. Amdahl, G. A. Blaauw and F. P. Brooks Jr., Architecture of the IBM System/360, IBM Journal of Research and Development, April 1964

参考文献

[編集]- ISCA: Proceedings of the International Symposium on Computer Architecture

- Micro: IEEE/ACM International Symposium on Microarchitecture

- HPCA: International Symposium on High Performance Computer Architecture

- ASPLOS: International Conference on Architectural Support for Programming Languages and Operating Systems

- ACM Transactions on Computer Systems

- IEEE Computer Society

- Microprocessor Report

- ヘネシー, ジョン; デイビッド・パターソン (1994年). コンピュータ・アーキテクチャ ― 設計・実現・評価の定量的アプローチ. 富田眞治(他訳). 日経BP社. ISBN 4-8222-7152-8

- タネンバウム, アンドリュー (2000年) (日本語). 構造化コンピュータ構成 第4版 デジタルロジックからアセンブリ言語まで. 長尾高弘(他訳). ピアソンエデュケーション. ISBN 4894712245

学習用の参考図書や文献

[編集]- 高橋茂:「ハードウェア工学概論:計算機アーキテクチャと構成方式」、ISBN 978-4-320-08476-6(1988年5月)。

- 高橋茂、工藤知宏:「計算機工学概論:計算機アーキテクチャと構成方式」、共立出版、ISBN 978-4320085275(1993年4月1日)。

- 中沢喜三郎:「計算機アーキテクチャと構成方式」朝倉書店、ISBN 978-4254121001(1995年11月)。

- 富田眞治:「コンピュータアーキテクチャー 第2版:基礎から超高速化技術まで」、丸善、ISBN 978-4-621047835(2000年8月)。

- 坂井修一:「コンピュータアーキテクチャ」、コロナ社、ISBN 978-4-339-01843-1 (2004年3月31日)。

- 城和貴:「コンピュータ アーキテクチャ-入門」、サイエンス社、ISBN 978-4-7819-1328-5 (2014年1月10日)。

- 堀桂太郎:「図解 コンピュータアーキテクチャ入門(第3版)」、森北出版、ISBN 978-4-627-82903-9 (2019年12月)。

- 坂井修一:「実践 コンピュータアーキテクチャ(改訂版)」、コロナ社、ISBN 978-4-339-02906-2 (2020年4月30日)。

- 馬場敬信:「コンピュータアーキテクチャ(改訂5版)」、オーム社、ISBN 978-4-274-22615-1 (2020年11月6日)。

- 鈴木健一:「よくわかる コンピュータアーキテクチャ」、森北出版、ISBN 978-4-627-85781-0(2024年9月)。

関連項目

[編集]外部リンク

[編集]- WWW Computer Architecture Page

- ESCAPE - コンピュータアーキテクチャ教育に利用可能なPC用シミュレーション環境

- A Practical Approach to Computer Systems Design and Architecture

- The von Neumann Architecture of Computer Systems

- コンピュータアーキテクチャ - 研究人材のためのe-learning(科学技術振興機構)

- コンピュータアーキテクチャの話 第1回(マイナビ連載記事)