VLIW

VLIWとはVery Long Instruction Word(超長命令語)の略で、マイクロプロセッサの内部設計(マイクロアーキテクチャ)の一つである。

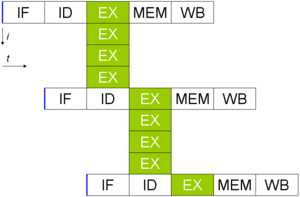

VLIWではロード、ストア、演算、分岐などの命令 (atom) 複数個からなる命令語 (molecule) を構成してそれを一度に実行する。それぞれの命令は依存関係を持たないことがコンパイラレベルで保証される。また依存性を除去できない場合はNOP(No Operation・何もしない)命令で補い、常に決まった数の命令がパイプラインに投入される(RISCに類似のパイプライン戦略)。「超長命令」の由来は命令語が通常128ビットなどの長い固定長を持つことによる。

スーパースカラやアウトオブオーダーと異なり、いったんパイプラインに乗った命令は並列性を分析する必要がない為、ハードウェアコストの低下や動作の高速化が期待される。反面、VLIWの性能を引き出すには並列性を検出する高度なコンパイラ技術が必要である。その意味でRISCよりもさらにソフトウェア寄りの設計を持つCPUアーキテクチャといえる。

VLIWは広くは普及せず、VLIWを改良した規格にEPICアーキテクチャがあるが、これも普及しなかった。

歴史

VLIWという用語とそのアーキテクチャの概念は、1980年代初期に当時イェール大学のジョシュ・フィッシャーによって考案された。彼は、ニューヨーク大学の大学院生のとき、トレーススケジューリングというVLIWのコンパイル技術を開発した。VLIWが発明される以前には、機能ユニットをあらかじめソフトウェアでスケジューリングし、命令レベルの並列化をするという考え方は、水平型マイクロコードの開発過程ですでに確立していた。フィッシャーの業績は、一般的なプログラミング言語で書かれたプログラムを、水平型マイクロコードに変換するコンパイラを開発したことにある。フィッシャーの行った研究によって、ワイドイシューなマシン上で良いパフォーマンスを出すためには、基本ブロックの中だけではなく、それを超えて並列性を探す必要があることが分かった。彼は、基本ブロックを超えた並列性を見つけるためのリージョンスケジューリングも開発した。トレーススケジューリングも、そうしたスケジューリングテクニックのひとつである。このスケジューリング技術は、最も起こりそうな基本ブロックの経路を最初にスケジューリングする。そして、次に、二番目に起こりそうな経路をスケジューリングするという風に、最後までスケジューリングしていく。それぞれのスケジューリングを行うとき、投機的な動作を扱うコードも必要に応じて、挿入する。

フィッシャーが行った二つ目の革新的な業績は、ターゲットCPUのアーキテクチャは、コンパイラに向くように設計されるべきで、VLIWのコンパイラとアーキテクチャは、協調設計されなくてはならないと概念を主張したことである。このことは、イェール大学でフィッシャーが浮動小数点システムFPS164のようなアーキテクチャ向けのコンパイラを作ることが難しかったという体験に基づいている。FPS164は、複雑な命令体系を持っているため、複雑なスケジューリングアルゴリズムを必要とした。フィッシャーは、セルフドレイン・パイプライン(self-draining pipelines)・広いマルチポートレジスタファイル・メモリアーキテクチャといったVLIWの設計を特徴付ける原則を開発していった。これらの原則によって、コンパイラが簡単に高速なコードを生成できる。

最初のVLIWコンパイラは、ジョン・エリスの博士論文(指導教授:フィッシャー)で述べられている[1]。 ジョン・ルッテンバーグもまた、スケジューリングに関するある重要なアルゴリズムを開発した。

1984年にイェール大学を離れたフィッシャーは、Multiflowというスタートアップ会社を設立した。そのときの共同創立者は、ジョン・オドネルとジョン・ルッテンバーグである。Multiflowは、TRACEシリーズというVLIWのミニコンを生産し、1988年頃に販売開始した。MultiflowのVLIWは、28演算を並列に実行できた。TRACEシステムは、MSI (Medium-Scale Integration) / LSI (Large-Scale Integration) / VLSI (Very Large-Scale Integration)という異なる技術を使って実装された。こうした異なる技術を混ぜることは、あまり評判が良くなく、いずれメモリ以外の部品がひとつのチップ上に実装されるようになる。Multiflowは、少し時代を先取りしすぎていたところがある。しかし、主な半導体会社は、Multiflowの技術の価値を認め、コンパイラやアーキテクチャのライセンスを取得していた。

後方互換性

シリコン技術が進み、より広い実行ユニットが実装できるようになったが、初期のVLIWプロセッサ用にコンパイルされたバイナリプログラムは、より広い実行ユニットをもつプロセッサでは、実行できない。なぜなら、VLIWの命令セットは、そのプロセッサの実行ユニット数に依存していたからである。

Transmetaでは、x86アーキテクチャのCrusoeという実装において、バイナリ・バイナリソフトウェアレイヤ(コードモーフィング)で後方互換性を維持しようとした。Crusoeは、基本的に、実行時にリコンパイル・最適化・x86のオペコードへの変換をCPU内部のマシンコードで行うと言われている。したがって、Crusoeは、内部的にはVLIWプロセッサであるといえる。

インテルのItaniumアーキテクチャでは、もっと一般的な方法で、後方互換性を維持しようとしている。1つの命令は、複数のオペコードを持ち、それぞれのオペコードが、その前のVLIW命令との依存関係を示すビットフィールドが割り当てられている。このビットは、コンパイル時に設定されるので、ハードウェアが依存関係を調べる必要がなくなる。また、こうした依存関係情報を命令列の中に埋め込むことで、実行ユニット数に依存しなくなる。つまり、プロセッサは実行ユニットがもつ分だけ、依存しない命令を並列実行すればよい。

もうひとつのVLIWアーキテクチャの欠点は、常にすべての実行ユニットを使うことができず、NOP命令を実行してしまうということである。これは、そのコード内にたくさんの命令の依存関係が存在する場合に起こる。

ひとつのチップ上にのせることができるトランジスタが増えるにつれて、VLIWのこうした欠点は、あまり重要でなくなってきている。VLIWは、アプリケーションごとにカスタマイズしたプロセッサを使用できる組み込み市場で人気が出てきている。組み込み向けVLIWプロセッサは、 富士通のFR-V、PixelworksのBSP15/16、STMicroelectronicsのST231、NXPのTriMedia[2]、CEVAのCEVA-X DSP、 Improv SystemsのJazz DSP、Silicon Hiveなど、多くのベンダーからリリースされている。また、テキサス・インスツルメンツのC6xxxファミリーのTMS320 DSPもVLIWということになる。

主なVLIWプロセッサ

- Apollo PRISM

- Intel i860

- Crusoe

- Itanium

- FR-V

- Radeon HDシリーズ (HD 2xxx、HD 3xxx、HD 4xxx、HD 5xxx)