FPGA

FPGA(英: field-programmable gate array)は、製造後に購入者や設計者が構成を設定できる集積回路であり、広義にはPLD(プログラマブルロジックデバイス)の一種である。現場でプログラム可能なゲートアレイであることから、このように呼ばれている。

概要

FPGAの構成設定は一般にハードウェア記述言語 (HDL) を使って指定し、その点はASICに近い。FPGAはASICで実装できる任意の論理機能を実装できる。出荷後に機能を更新でき、設計面で部分的に再構成でき[1]、ASIC設計よりエンジニアリングコストが低い点などが多くの用途で利点となる[2]。

FPGAに含まれるプログラム可能な論理コンポーネントを「論理ブロック」などと呼び、それら論理ブロック間を相互接続する再構成可能な配線階層がある。この構成によっていわばワンチップのプログラム可能なブレッドボードの役目を果たす。論理ブロックを組み合わせて複雑な論理回路を構成することもできるし、単にANDゲートやXORゲートのような単純な論理回路を構成することもできる。多くのFPGAでは、論理ブロックにメモリ要素も含んでおり、単純なフリップフロップまたはより完全なメモリブロックで構成されている[2]。

デジタル回路機能に加え、一部のFPGAはアナログ回路要素も持っている。最も典型的なアナログ機能としては、スルーレートや出力ピンの駆動強度などを設定できるものが多く、負荷の小さいピンのスルーレートを遅くすることでオーバーシュートを防いだり、負荷の大きいピンのスルーレートを速くすることで転送レートを高速化する[3][4]。もう1つのよくあるアナログ機能としては、入力ピンに付属した差動コンパレータがあり、差動信号チャンネルに接続するよう設計されている。さらに、ADCとDAC、アナログ信号処理ブロックまで搭載し、システム・オン・チップを構成できるよう意図されたFPGA(ミクスド・シグナルFPGA)もある[5]。全体がアナログ回路でFPGAのように配線を再構成可能なFPAA[6]もあり、ミクスド・シグナルFPGAはFPGAとFPAAの中間的存在である。

歴史

FPGA業界はPROMとPLD(プログラマブルロジックデバイス)から発展した。PROMもPLDも出荷後に顧客企業の工場でまとめてプログラムできるが、プログラム可能なロジックは論理ゲート間に固定の配線を行うものだった[7]。

プログラム可能なロジックアレイ、論理ゲート、論理ブロックといった基本概念は1985年、David W. PageとLuVerne R. Petersonの取得した特許に既に見られる[8][9]。

ザイリンクスの共同創業者ロス・フリーマンとベルナルド・フォンデルシュミットは1985年、世界初のFPGA XC2064を製品化した[10]。XC2064はプログラム可能な論理ゲートとプログラム可能な配線を持っていた。これにより、新たなテクノロジーとその市場が始まった[11]。XC2064は64個の構成可能論理ブロック (CLB) で構成され、それぞれのCLBには3入力ルックアップテーブル (LUT) があった[12]。その二十数年後、Freemanは発明者殿堂入りを果たした[13]。

1980年代後半、アメリカ海軍が60万個の再プログラム可能な論理ゲートでコンピュータを構成するというスティーブ・キャセルマンの提案した実験に資金提供した。キャセルマンはこの開発に成功し、1992年に関連特許を取得した[7]。

ザイリンクスは1985年から1990年代中ごろまで急激に発展したが、そのころから競合企業が急成長し、市場シェアを浸食し始めた。1993年にはActel(現Microsemi)のシェアが18%にまで増大した[11]。

1990年代、FPGAは微細化と生産量の両面で大きく発展した。1990年代初め、FPGAは主に通信業やネットワークに使われていた。90年代末にはコンシューマ市場、自動車、産業用途にまで使われるようになっていた[14]。

1997年、サセックス大学の研究者エイドリアン・トンプソンが遺伝的アルゴリズムとFPGAを組み合わせた音声認識装置を開発し、FPGAに注目が集まった。トンプソンは、ザイリンクス製の10×10セルのFPGAのアナログ機能を利用して、2つの音を識別できるよう学習するハードウェアを開発したものである。このような遺伝的アルゴリズムをFPGAのようなデバイスの構成に使う方式は、進化型ハードウェアと呼ばれるようになっている[15][7]。

最近の発展

最近では、FPGAにCPUコアや関連する周辺回路を組み込み、完全な「プログラム可能なチップ上のシステム」を実現する製品も登場している。例えば、ザイリンクスはPowerPCプロセッサを組み込んだFPGAとしてVirtex-II PROおよびVirtex-4を発売している。Atmel FPSLICも同様の製品で、Atmel AVRプロセッサを組み込んでいる。アクテルのSmartFusionはARMアーキテクチャのCortex-M3のCPUコアを組み込んでいる。

これとは別の流れとして、ソフトプロセッサコアをFPGA上に構成して利用する方式もある。

現在のFPGAの多くは動作中にも再構成可能であり、そこから再構成可能コンピューティングという考え方も生まれた。これはシステムがそのとき実行しようとしているタスクの傾向に沿って自らを再構成するという考え方である。例えば、ミトリオニクス社の「ミトリオン・バーチャル・プロセッサー」[16]はFPGA上に実装された再構成可能なソフトプロセッサである。ただし、これは実行中の動的再構成はできない。

FPGAとも異なる新たなアーキテクチャも登場しつつある。Stretch S5000はソフトウェアから構成可能なマイクロプロセッサで、CPUコアのアレイとFPGA風のプログラム可能なコアを同じチップに搭載している[17]。

ゲート数

- 1987年: 9,000ゲート、ザイリンクス[11]

- 1992年: 600,000ゲート、Naval Surface Warfare Department[7]

- 2000年代初頭: 数百万ゲート[14]

市場規模

- 1985年: 世界初の商用FPGAが開発された(ザイリンクス)[11]

- 1987年: 1400万ドル[11]

- 1993年ごろ: 3億8500万ドル以上[11]

- 2005年: 19億ドル[18]

- 2010年: 40億ドル[19]

- 2020年: 85億ドル(予想)[20]

FPGAを使った設計件数

FPGAの比較

従来、FPGAはASICに比べて低速でエネルギー効率が悪く、実装可能な機能も限られていた。しかし、大量生産、製造ルールの微細化、研究開発などにより、ASICとFPGAの性能差はかなり縮まっている[24]。

バグ修正が現場で可能な点、開発・製造期間が短くて済む点などが利点である。また、設計段階ではFPGAを使い、最終的に設計が確定したらASICなどに移行して生産するという手法も可能である。

ザイリンクスは最近ではこのFPGAとASICの関係が一部市場で変化してきたと主張している[25]。

- 集積回路のコストが占める割合はどんどん上昇している。

- ASICは開発期間とコストを押し上げる要因となっていた。

- 研究開発部門の人材は減ってきている。

- 市場の変化が激しくなり、タイムリーな製品投入ができないと利益が上がらなくなってきた。

- 経済状況が悪化し、低コストのテクノロジーが重視されるようになってきた。

これらの傾向から、大量生産ならASICという観念が通用しなくなり、FPGAを採用することが多くなってきた[25]。

一部のFPGAは一部が動作中に残りの部分を再構成できる動的再構成の機能を持っている。

CPLDとの比較

CPLDとFPGAの大きな違いはアーキテクチャである。CPLDの方が構成の自由度が小さいが、遅延時間が予測しやすく、チップ面積における相互接続用経路の比率も小さい。FPGAは逆に相互接続の方が支配的で、それゆえに柔軟性が高い。

また、FPGAの方が組み込まれている機能が高度でメモリも埋め込まれており、デコーダや数学関数の演算を実装した論理ブロックもある。

セキュリティ

セキュリティの観点ではFPGAにはASICや通常のマイクロプロセッサと比べて長所と短所がある。装置の製造(組み立て)段階で悪意ある細工をしようとしても、FPGAではそれが具体的にどう動作するのかハードウェアを見ただけではわからず、そのようなリスクが低くなる[26]。一方で、コンフィギュレーションをロードする際に傍受される危険性があるため、ビットストリームの暗号化をサポートするFPGAもある。

用途

FPGAの用途としては、デジタル信号処理、ソフトウェア無線、アビオニクス、ASICのプロトタイピング、医用画像処理、コンピュータビジョン、音声認識、暗号、バイオインフォマティクス、コンピュータハードウェアのエミュレータ、電波天文学、金属探知機など多岐にわたる。

FPGAは本来CPLDと競合するものとして、プリント基板上のグルー・ロジックを対象としていた。その後、規模や機能や性能が向上するにつれ、扱う機能範囲が拡大していき、システム・オン・チップとしてマーケティングされるまでになった。特に1990年代後半にFPGAに独立した乗算器が組み込まれると、それまでDSPが扱っていた分野にまでFPGAが採用されるようになっていった[27][28]。

FPGAは特に高い並列性が期待できる分野やアルゴリズムの実装で威力を発揮する。例えば暗号解読がその典型例で、総当り攻撃の実装にはFPGAが適している。

暗号化や動画の圧縮、伸張、画像処理、ニューラルネットワーク処理などのロジックをチップ内部に持てるようになり、特定の用途の処理を高効率かつ高速化が可能になる[29]。一例としてマイクロプロセッサーとFPGAで電力当たりの性能を比較した場合、検索処理では約10倍、複雑な金融モデルの解析では実に約25倍もFPGAの方が性能が高いとされる[30]。

FPGAは高性能計算用途にも採用されつつあり、高速フーリエ変換や畳み込みといった演算をマイクロプロセッサとソフトウェアの代わりにFPGAで実装するといった使い方がなされている。

FPGAの論理リソースは本質的に並列動作可能であるため、クロック周波数が低くても計算時間を大幅に短縮できる可能性がある。またFPGAの柔軟性を利用すれば、演算精度と同時に動作する演算ユニット数のトレードオフにより、さらに高い演算性能を達成できる。ここから時間のかかる計算をソフトウェアからFPGAに肩代わりさせるという考え方が生まれ、再構成可能コンピューティングと呼ばれるようになった。

ソフトウェアに比べてFPGAの構成の設計は複雑で時間がかかることから、高性能計算におけるFPGAの採用は限定的なものとなっている。

従来からFPGAは生産量の少ない特定分野向け用途で使われてきた。生産量が少ない場合、ASICよりもFPGAの方がコストが低くなる。近年はこの境目が変化しつつあり、FPGAの方がコストと性能の面でASICよりも優れているという範囲が広がってきている。

並列計算でない用途としては、異なる信号規格どうしの回路信号の変換器としての用途もある[31]。

アーキテクチャ

典型的なFPGAのアーキテクチャは[2]、論理ブロックの配列(Configurable Logic Block, CLB あるいは Logic Array Block, LAB などメーカーによって正式呼称は異なる)、I/Oパッド、配線用チャンネルから構成される。一般に配線用チャンネルは全て同じ幅(導線の本数)で、複数のI/Oパッドが論理ブロックの1行の幅または1列の高さに対応するようになっている。

アプリケーション回路は適正なリソースを用いてFPGA内に配置される。設計から必要な論理ブロック数やI/O数は容易に決定できるが、使用する論理ゲート数が同じであっても設計によって配線量は大きく異なる。例えば同じ論理ゲート数でも、クロスバースイッチはシストリックアレイよりも多くの配線が必要である。使われない配線が多いと、性能も低下するし未使用部分が増えてしまうため、FPGA製造業者は論理ブロック数やI/O数にちょうど見合った配線を用意するよう最適化を心がけている。この配分を決定するためにRent's ruleを使ったり、既存の回路設計で実験したりしている。

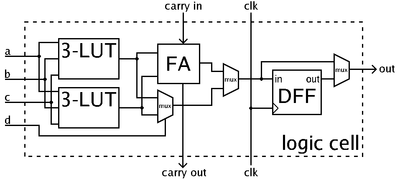

一般に論理ブロックはいくつかの論理セル(ALM、LE、スライスなどと呼ぶ)で構成される。典型的な論理セルは下図にあるように、4入力ルックアップテーブル (LUT)、1つの全加算器 (FA)、D型フリップフロップなどから構成される。この図ではLUTは2つの3入力LUTで構成されている。通常モードでは、左のマルチプレクサ (mux) を通して4入力LUTを構成している。演算モードでは、LUTの出力がFAに入力される。モード選択は中央のmuxでプログラムされる。出力は同期/非同期を選択でき、図では左端のmuxのプログラムで選択できる。実際にはスペースを節約するため、FAの機能の一部または全部をLUTに組み込むこともある[32][33][34]。

この図のような論理セルを2つまたは4つでALMやスライスを構成し、入力を共有させる。

論理ブロックは一般にALM/LE/スライス数個で構成される。

最近では高性能FPGAに6入力LUTを採用する例がある[35]。

クロック信号(および高ファンアウト出力信号など)は、商用FPGAでは通常とは異なる配線でルーティングされ、通常の信号とは別に管理される。

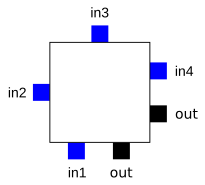

上の例での論理ブロックのピン配置の例を次の図に示す。

入力が論理ブロックの4つの面にひとつずつあるのに対して、出力は右と下の2箇所で配線と繋ぐことができる。配線は複数本並んでいて、出力はそれらの任意の線に接続可能である。同じことはI/Oパッドにも言える。チップ上端のI/Oパッドは上端に隣接するW本の配線のいずれとも接続可能である。

一般にFPGAの配線は分割されていない。すなわち、配線セグメントは論理ブロック1つぶんをまたぐ長さで縦の配線と横の配線が交差するスイッチボックスとスイッチボックスの間を走っている。そして、スイッチボックス内のプログラム可能なスイッチをオンにすることでさらに配線が続くことになり、そのようにして長い配線を構築する。高速化のために複数の論理ブロックをまたぐような長い配線を最初から用意しているFPGAアーキテクチャもある。

垂直な配線と水平な配線が交差する箇所にスイッチボックスがある。下の図では、水平と垂直にそれぞれ3本の線があり、その交点3カ所にプログラム可能なスイッチ群がある。交点すべてにスイッチを配するとコストがかかり遅延も大きくなるため、このように斜めの交点にだけスイッチを配するのが一般的である。どの交点にスイッチを配するかはいくつか方式がある。1つの交点には6つのプログラム可能なスイッチがある。

最近のFPGAはこれにさらに高機能な論理ブロックを加えるなどしている。高機能ブロックを埋め込むことで、一からその機能を構成するよりも必要な面積を削減でき、かつ性能が向上する。例えば、乗算器、汎用DSPブロック、汎用CPUコア、高速I/Oロジック、メモリなどが埋め込まれたFPGAがある。

FPGAの設計とプログラミング

FPGAの動作を定義するには、ユーザーがハードウェア記述言語 (HDL) または回路図で設計を提供する。大規模な場合は回路図よりもHDL方式の方が適している。しかし、回路図の方が設計の視覚化が容易で事前に確認しやすい場合もある。

HDLで記述した設計をEDAツールに入力し、ネットリストを生成する。ネットリストを実際のFPGAアーキテクチャに対応させるため、そのFPGAのメーカーが提供しているPlace and routeと呼ばれるソフトウェアを使用する。ユーザーはその結果をシミュレータにかけるなどして、タイミングに問題がないかなどを検証する。設計と検証が終わったら、バイナリファイルを生成し(この工程もFPGAメーカーの独自ソフトウェアを使う)、FPGAの(再)構成に使う。バイナリファイルはシリアル通信 (JTAG) 経由でFPGAに転送するか、EEPROMなどの外部メモリデバイスに格納する。

最も一般的なHDLとしてはVHDLとVerilogがあるが、これらは通常のプログラミング言語で言えば抽象度がC言語を少し下回る程度であり、手間がかかる。そこでもっと高い抽象度でハードウェア設計を行う言語を導入する動きもある。

FPGAにおける複雑なシステムの設計を単純化するため、検証・最適化済みの既存の機能ブロックや回路をライブラリ化して利用する。このような既存の回路をIPコアと呼び、FPGAベンダーやサードパーティのIP業者から購入できる(一般に無償ではない)。他にもOpenCoresといった開発者コミュニティなどでフリーなものが入手できる。

FPGAアプリケーションを開発する場合、設計の各段階でシミュレーションによる検証を行う。まずVHDLやVerilogのRTL記述でシミュレーションを行う。次に論理合成によって出力されたネットリスト、ネットリストを変換したゲートレベル記述でもシミュレーションによる検証を行う。そこからさらにFPGA向けに配置を決定すると配線による遅延が加わるため、再度シミュレーションによる検証が必要になる。

基本プロセス技術の種類

- SRAM - システム内で再プログラム可能。外部ブートデバイスが必要。CMOS。

- アンチヒューズ型 - 一度だけプログラム可能。CMOS。

- PROM - 一度だけプログラム可能。

- EPROM - 一度だけプログラム可能。ただし窓付きであれば紫外線照射で消去できる。CMOS。

- EEPROM - 消去可能。一部にはシステム内でプログラム可能なものもある。CMOS。

- フラッシュメモリ - 消去可能。一部にはシステム内でプログラム可能なものもある。一般にフラッシュセルの方がEEPROMセルより小さく、製造コストが小さい。CMOS。

- ヒューズ型 - 一度だけプログラム可能。バイポーラ。

主なメーカー

FPGA市場を主導しているのはザイリンクスとアルテラで、両社は長年のライバル関係にある。両社のシェアを併せると市場の80%を占め[36]、2009年まではザイリンクス単独で50%程度占めていた。2012年にはアルテラがザイリンクスに売上高で肩を並べるとの予想もある[37]。2010年にアルテラが急成長し、売り上げが12億米ドルから20億米ドルへと急成長した[38]。

ザイリンクスもアルテラもWindowsおよびLinuxで動作する設計用ソフトウェアを無料で提供している[39][40]。

なお、アルテラについては 2015年6月1日 にインテルによる買収[41]、ザイリンクスについては (現地時間の)2020年10月27日にAMDとの買収合意[42]が発表された。

他に以下のような企業がFPGAを開発・製造している。

- ラティスセミコンダクター

- マイクロセミ

- クイックロジック (QuickLogic)

- アクロニクス

関連項目

脚注・出典

- ^ Wiśniewski, Remigiusz (2009). Synthesis of compositional microprogram control units for programmable devices. Zielona Góra: University of Zielona Góra. pp. 153. ISBN 978-83-7481-293-1

- ^ a b c FPGA Architecture for the Challenge

- ^ FPGA Signal Integrity tutorial

- ^ NASA: FPGA drive strength

- ^ Mike Thompson. Mixed-signal FPGAs provide GREEN POWER. EE Times, 2007-07-02.

- ^ 英: field-programmable analog array

- ^ a b c d History of FPGAs

- ^ Google Patent Search, "Re-programmable PLA". Retrieved February 5, 2009.

- ^ Google Patent Search, "Dynamic data re-programmable PLA". Retrieved February 5, 2009.

- ^ Peter Clarke, EE Times "Xilinx, ASIC Vendors Talk Licensing" June 22, 2001. Retrieved February 10, 2009.

- ^ a b c d e f Funding Universe. “Xilinx, Inc.” Retrieved January 15, 2009.

- ^ Clive Maxfield, Programmable Logic DesignLine, "Xilinx unveil revolutionary 65nm FPGA architecture: the Virtex-5 family". May 15, 2006. Retrieved February 5, 2009.

- ^ Press Release, "Xilinx Co-Founder Ross Freeman Honored as 2009 National Inventors Hall of Fame Inductee for Invention of FPGA"

- ^ a b Clive Maxfield, book "The Design Warrior's Guide to FPGAs" Published by Elsevier, 2004. ISBN 0750676043, 9780750676045. Retrieved February 5, 2009

- ^ “Original Paper on Work, Thompson”. 2010年7月29日閲覧。

- ^ 英: Mitrion Virtual Processor

- ^ S5000ソフトウェア・コンフィギュラブル・プロセッサ Stretch

- ^ Dylan McGrath, EE Times, "FPGA Market to Pass $2.7 Billion by '10, In-Stat Says". May 24, 2006. Retrieved February 5, 2009.

- ^ Moshe Gavrielov, Electronics Weekly, "FPGA Market Soaring To $4bn In 2010, says Gavrielov". May 19, 2010. Retrieved January 8, 2013.

- ^ Research and Markets, "Field-Programmable Gate Array (FPGA) Market by Architecture, Configuration, Application, and Geography - Trends & Forecasts From 2014 – 2020". January, 2015. Retrieved March 20, 2015.

- ^ Narinder Lall, eASIC Corporation, "FPGA Judgment Day: Rise of Second Generation Structured ASICs". March, 2008. Retrieved February 5, 2009.

- ^ Dylan McGrath, EE Times, "Gartner Dataquest Analyst Gives ASIC, FPGA Markets Clean Bill of Health". June 13, 2005. Retrieved February 5, 2009.

- ^ Virtex-4 Family Overview

- ^ Bob Pencek, Industrial Embedded Systems, "Reconfigurable Application-Specific Computing: How Hybrid Computer Systems using FPGAs are Changing Signal Processing". No Date. Retrieved February 5, 2009.

- ^ a b Tim Erjavec, White Paper, "Introducing the Xilinx Targeted Design Platform: Fulfilling the Programmable Imperative." February 2, 2009. Retrieved February 2, 2009

- ^ Huffmire Paper "Managing Security in FPGA-Based Embedded Systems." Nov-Dec 2008. Retrieved Sept 22, 2009

- ^ FPGA/DSP Blend Tackles Telecom Apps

- ^ Xilinx aims 65-nm FPGAs at DSP applications

- ^ インテル、FPGA大手のアルテラ買収を完了

- ^ インテル「2兆円買収」で手に入れる3つの未来

- ^ トランジスタ技術スペシャル編集部(編著: 森田一ほか)および大中邦彦(該当22ページの著者)、『トランジスタ技術スペシャル』、CQ出版社、22ページ図7(ページ右上にある)、2009年7月1日発行。

- ^ Cyclone II Architecture ALTERA

- ^ Section I. Device Core ALTERA

- ^ Virtex-4 FPGA User Guide Xilinx

- ^ Achieving Higher System Performance with the Virtex-5 Family of FPGAs Xilinx

- ^ Seeking Alpha, "Altera and Xilinx Report: The Battle Continues". July 17, 2008. Retrieved February 5, 2009.

- ^ EE Time 2011年03月15日記事

- ^ Altera Corporation 2010 Letter to Shareholders

- ^ “Xilinx ISE WebPACK”. 2010年7月29日閲覧。

- ^ “Quartus II Web edition software”. 2010年7月29日閲覧。

- ^ CNET Japan 2015年6月2日

- ^ “AMD、競合のXilinxを350億ドルで買収 Intelと競合するデータセンター事業強化”. ITmedia NEWS. 2020年12月30日閲覧。