ANDゲート

| 入力 | 出力 | |

| A | B | A AND B |

| L | L | L |

| L | H | L |

| H | L | L |

| H | H | H |

ANDゲート(アンドゲート)は論理積の論理ゲートである。

概要[編集]

右に挙げた真理値表に従った動作をする。出力がHighとなるのは、ANDゲートの両方の入力がHighの場合のみである。

ANDゲートの入力の一方のみがHighの場合やどちらもHighでない場合、出力はLowとなる。換言すれば、ANDゲートは2つの入力から最小値を求めるものである。逆にORゲートは最大値を求める。

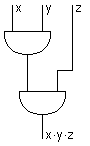

3入力ANDゲート[編集]

入力端子が3つの3入力ANDゲート(英: Triple 3-Input AND gate)も存在する。

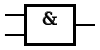

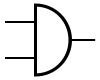

記号[編集]

ANDゲートを表す記号は3種類(ANSI、IEC、DIN)ある。

|

|

|

| MIL/ANSI 記号 | IEC 記号 | DIN 記号 |

ANDゲートの入力を A と B、出力を C とすると、 という論理式を実装していることになる。

実装[編集]

|

上図はNMOSによる実装例である。a と b が入力、F が出力である。

代替技法[編集]

ANDゲートがない場合でも、NANDゲートやNORゲートからANDゲートを構成できる。NANDゲートとNORゲートは「汎用ゲート」であり[1]、他のあらゆる種類の論理ゲートを構成できる。XORゲートでもANDゲートを構成できるが、そのような使い方をすることは滅多にない。

脚注・出典[編集]

- ^ Mano, M. Morris and Charles R. Kime. Logic and Computer Design Fundamentals, Third Edition. Prentice Hall, 2004. p. 73.