ラッチ回路

ラッチ回路(ラッチかいろ)は、双安定マルチバイブレータの一種で、1ビットの情報を保持できる状態を有する電子回路である。

概要

[編集]アナログ回路の応用もあるが、デジタル回路(論理回路)のひとつとみなされることもある。クロックのある(同期・クロックド)ラッチでは、クロックのエッジ位置でのみ出力が変化するエッジトリガタイプと、「オープン」の期間は素通りするトランスペアレントタイプの2種類に大別される。

用語には揺れがあり、エッジトリガタイプをフリップフロップとし、トランスペアレントタイプのみをラッチとする用法もある。また、エッジトリガタイプを同期式フリップフロップ、セット・リセットとトランスペアレントタイプを非同期式フリップフロップ、などとすることがある。

ラッチを含む回路は状態を記憶することができ、出力は状態と入力の組み合わせで決まる。このような回路を順序回路と呼ぶ。

近年の高速なアナログ回路では、コンパレータや分周回路として差動のラッチ回路が数多く利用される。

セット・リセット型ラッチ回路

[編集]SRラッチ/双安定性ラッチ

[編集]

最も基礎的なラッチが「SRラッチ」(あるいはRS-)である。Sは「Set」、Rは「Reset」の意である。

一般的な論理ゲートでの実装としては、たすきがけになったペアのNORゲートで構成する。状態は、右の図などでQの記号を付した端子から出力される。NANDゲートでも(少し動作が変わるが)同様の状態を持つ回路を構成できる(後述)。

また、論理でなく電子回路的な、言い換えるとアナログ的に調整された設計が必要になるが、インバータ2つなどによる構成もある[1][2]。

SとRの記号を付した端子が入力であり、それぞれ前述の通り「Set」と「Reset」である。両方ともLowの時、たすきがけ配線のフィードバック作用による双安定性により、 QとQの出力が、それぞれLowかHighのどちらか、かつ、互いに逆の状態に保たれる。

R (Reset) がLowの間に S (Set) がHighとなった場合、Q出力がHighとなり、SがLowに戻った後も QはHighを保持する。同様に、SがLowの間に RがHighとなった場合、Q出力がLowとなり、RがLowに戻った後も QはLowを保持する。

| SR ラッチ動作[3] | ||||||||

|---|---|---|---|---|---|---|---|---|

| 状態遷移表 | 励起表 | |||||||

| S | R | Qnext | 動作 | Q | Qnext | S | R | |

| Low | Low | Qprev | 保持 | Low | Low | Low | X | |

| Low | High | Low | リセット | Low | High | High | Low | |

| High | Low | High | セット | High | Low | Low | High | |

| High | High | -- | 禁止 | High | High | X | Low | |

(この表において、Xはdon't care)

SとRを両方ともHighにした場合の動作は一般には不定であり、「禁止」とされている場合もある(上記の表では安全側をとり禁止とした)。次の節で説明する。

SRラッチの「不定」

[編集]SとRの入力を両方ともHighにした場合については、一般に「不定」とされることが多い。ICの品種によっては、その内部構造などの理由により「禁止」とされている場合もあり、その場合は絶対にそのような入力を与えてはならない(MUST NOT)。一方で汎用論理ICと配線により自作した回路などでは、電子回路として意図的にそのような場合の動作を利用することもある。具体的には、両方をほぼ同時にLowにした場合に、その変化速度のわずかな違いによってどちらが早かったかを検出する回路という応用がある。クロック等を必要とせず、ハードウェアによる検出であるため確実度が高い。いずれにしても、「不定という状態」があるわけではない。

NORゲートで構成されたSRラッチの場合、入力を両方ともHighにすると、QとQの両方の出力が同時に、かつ過渡的にでなく[nb 1]Lowになる。Q = not Q という恒等式が成立していなければならない回路の場合(両方の出力を相補的に利用しているなど)、それに違反することになる。

ラッチとして集積されているICなどでは、内部が必ずしもNORゲートで構成されているとは限らず、実装によっては出力が安定する前に、長い振動状態を起こす危険もある(en:Metastability in electronics)。

この「不定」に、出力を 切り替える(トグルする) という状態を割り当てたものと見ることができるのが、#JKラッチである。

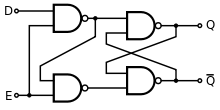

NANDによるバリエーション

[編集]

前述の構成をNANDゲートに置き換えたものである。入力はSとRどちらも負論理となり、オーバーラインを付してSとRと示している。それ以外の動作や禁止についてはNORによるものと同様である。

負論理の不便性などにもかかわらず、SRラッチは、歴史的に広く使われてきた。これは、論理方式によっては(たとえばCMOS以前のDTLやTTLなど)NANDのほうが簡単なため安価に生産できたためである。CMOS論理方式でもNMOSとPMOSの特性の非対称性により、NANDのほうが少し有利である。

|

| ||||||||||||||||||||||

JKラッチ

[編集]

JKラッチは、クロックを持つこともありJKフリップフロップと言われることも多い。

JKラッチは、次の状態を持つ。

|

| |||||||||||||||||||||||||

したがって、JKラッチは、SRラッチにおいては不定となる入力に対して、出力を 切り換える(トグルする) ような動作をする。

ゲーテッド・ラッチ回路と条件付通過性

[編集]ラッチは、データを通過するように設計されている。すなわち、入力信号が変化するとすぐに出力信号が変化する[nb 2]。あるいは、一方の信号が入力されていない時に非透過にするための簡単な論理(例えば「Enable」入力)を、通過性のラッチに追加することができる。

このようにすることにより、 通過性の低い ラッチや エッジで動作する フリップフロップなどを実装することができる[4]。

ゲーテッドSR型ラッチ回路

[編集]

同期SRラッチ(しばしばクロックドSRラッチ と呼ばれる)は、SRラッチへ2段目のNANDゲートを追加する(あるいはSRラッチに2段目のNORゲートを追加する)ことによって作ることができる。

そして、余分なゲートがさらに入力を逆にするので、単純なSRラッチがゲーテッドSRラッチになる(逆に、単純なSRラッチは、負論理のイネーブルつきのゲーテッドSRラッチとなる)。

EがHighのとき(イネーブル が真のとき)、信号は入力ゲートを通り抜け、内部のラッチにデータが伝わる。次に、「(0,0) = 保持」以外のすべての組み合わせでは、(Q,Q) がすぐに出力される。すなわち、このラッチは通過型である。

EがLowのとき(イネーブル が偽のとき)、ラッチは 閉じられて いて、出力は E が High のときの値を保持する。

イネーブル 入力はしばしばクロック信号となり、リードやライトのストローブ信号にもなる。

|

|

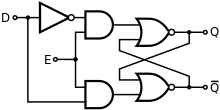

ゲーテッドDラッチ回路

[編集]

このラッチは、ゲーテッドSRラッチに密接に関連しており、同じようにして構成することができる。また、このラッチは 通過型ラッチ、データラッチ、あるいは単に ゲーテッドラッチ と呼ばれる。

Dラッチには、データと イネーブル の入力信号がある(イネーブルは、しばしば クロック または コントロール と呼ばれることがある)。通過型 という言葉は、イネーブル入力がOnのとき、入力Dからの信号が出力Qまで直接伝播することから付けられている。

通過型ラッチの典型的な使用例としては、I/Oポートや非同期回路がある[nb 3]。1つの回路あたりの通常複数のラッチを用いて、集積回路を構成することができる。一般的な7400シリーズの例として、通過型ラッチが4素子入った 74HC75 がある。

|

|

真理値表は、enable/clock 入力が0のとき、D入力は出力に影響を与えないことを示している。また、E/C入力がHighのとき、出力はDに等しい。

ゲーテッド・トグル型ラッチ回路

[編集]ゲーテッド・トグル型ラッチ回路は、前の状態を切り換える(トグルする)もうひとつの同期SRラッチである。

Tラッチ(Tフリップフロップと呼ばれることが多い)は、トグル (T) 入力がHighなら、クロック入力がストローブされると状態が変化(「トグル」)する。

Tラッチを表す論理式は、 Qnext = T ⊕ Qpre である。ここで、 Qnext は次の状態であり、 Qprev は前の状態を示している。

|

|

Tフリップフロップは、JKフリップフロップを使って作ることができる(具体的には、TがJとKピンを接続することによって実装される)。

また、Dフリップフロップを使用してTフリップフロップを作ることもできる(具体的には、T入力とQpreviousを、XORゲートを通してD入力に接続する)。

高速アナログ回路でのラッチ回路

[編集]

「ラッチ回路内部にあるクロスカップル部分の2つの信号線間に、微小な電位差があると、時間の経過とともにその電位差が開いていく」という特徴を利用して、コンパレータを高速化するために、ラッチ回路がしばしば用いられる。

コンパレータとしてラッチを使用する場合、前段へのキックバックノイズの影響を考慮しておく必要がある[5][6]。

ラッチ回路は高速なADコンバータなどに応用される。ADコンバータでは、コンパレータの速度がサンプリング周期を決定する重要な要因[7]であり、Flash ADCなど複数のコンパレータが必要な場合に、回路面積の削減と高速化のためにラッチ回路を利用できる。

差動型のDラッチは、分周回路を構成するために用いられる。ダイナミック・ラッチ・コンパレータやトラック・アンド・ラッチ・コンパレータは差動型Dラッチとみなせる。

ダイナミック・ラッチ・コンパレータ

[編集]

右図は、インバータと、スイッチを用いて、ダイナミック・ラッチを構成した回路である。

イネーブル信号 CK に High が入力されているとき、クロスカップル部にある2つのインバータの出力がHi-Zとなり、DとDからの入力が、ZとZへ伝えられる。

イネーブル信号 CK が Low になると、入力信号DとDからのスイッチが Off となり、クロスカップル部にある2つのインバータ(ラッチ回路)が動作する。

DとDの電位差が小さい場合でも、クロスカップル部分の動作が開始すると、ZとZの電位差が徐々に大きくなり、1ビットの情報がラッチされるため、離散時間でのコンパレータとなる。

ZとZの電位差は、 、 で与えられる[5]ため、前段にプリアンプを追加するなどして、初期値 Vin をできる限り大きくするか、クロスカップル部にある寄生容量 C を小さくするなどにより、応答速度の改善を図る。

トラック・アンド・ラッチ・コンパレータ

[編集]

トラック・アンド・ラッチ・コンパレータは、ネガティブインダクタンス回路を用いて、電流を操作し、ラッチ状態を作り出す回路である[9]。 このコンパレータはバイポーラとCMOSの両方で高速動作を実現でき[10][11]、高速のADコンバータなどに利用されている[12]。

分周回路

[編集]

差動Dラッチを2段組み合わせると2分周回路を作ることができる。これはシングルエンドのDラッチからDフリップフロップを構成する場合と同じである。

脚注

[編集]注釈

[編集]出典

[編集]- ^ Two Inverters Create A Versatile SR Flip-Flop With No NAND/NOR Gates2023年9月8日閲覧。

- ^ C-MOSインバータを使ったラッチ回路2例 - ウェイバックマシン(2016年4月13日アーカイブ分)2023年9月8日閲覧。

- ^ Roth, Charles H. Jr. "Latches and Flip-Flops." Fundamentals of Logic Design. Boston: PWS, 1995. Print.

- ^ Vojin G. Oklobdzija著 「The Computer Engineering Handbook」

- ^ a b 谷口研二著 「CMOSアナログ回路入門」 CQ出版 第8章 ISBN 978-4-7898-3037-9

- ^ PM Figueiredo, JC Vital, "Low kickback noise techniques for CMOS latched comparators", Circuits and Systems, 2004. ISCAS'04

- ^ a b B.J.McCarroll, C.G.Sodini, H.S.Lee, "A High-speed CMOS Comparator for Use in an ADC", IEEE SSC, Vol.23, No.1, 1988

- ^ P.Cusinato, M.Bruccoleri, D.D.Caviglia, and M.Valle, "Analysis of the Behavior of a Dynamic Latch Comparator", IEEE Tran. Circuits and Systems-I, Vol.45 No.3, 1998

- ^ "High speed latching comparator using devices with negative impedance" US Patent 51401882023年9月8日閲覧。

- ^ a b Behzad Razavi著 黒田忠広監訳,「RFマイクロエレクトロニクス」p.317 丸善 2002 ISBN 4-621-07005-3

- ^ F.P.Cortes, A.Girardi and S.Bampi, "Track-and-Latch Comparator Design Using Associations of MOS Transistors and Characterization", IEEE ICECS 2006

- ^ KL Shepard, Y Zheng, "On-chip oscilloscopes for noninvasive time-domain measurement of waveforms", IEEE ICCD 20012023年9月8日閲覧。

関連記事

[編集]参考文献

[編集]- Enoch Hwang, "Digital Logic and Microprocessor Design with VHDL", Thomson, 2006, ISBN 0-534-46593-5

- Fundamentals of Digital Logic by Brown and Vranesic

- S.P.Vingron: `Switching Theory. Insight through Predicate Logic.' Springer Verlag, 2003. ISBN 3-540-40343-4 — extensively covers the theory of latches

- Parallel Port Output expanding with Latches - ウェイバックマシン(2019年11月9日アーカイブ分)2023年9月8日閲覧。

- CircuitDesign.info: You want latches? We got latches CMOS D flip-flop design 2023年9月8日閲覧。