NORゲート

| 入力 A B |

出力 A NOR B | |

| L | L | H |

| L | H | L |

| H | L | L |

| H | H | L |

NORゲートは否定論理和の論理ゲートであり、その(論理的な)動作は、否定論理和すなわち、全ての入力の論理和(OR)をとったものの反転(NOT)である。つまり、全ての入力がLowの場合のみ出力がHighになり、Highの入力がひとつでもある場合はLowを出力する。

NANDゲート(否定論理積)と同様 functional complete である(詳細は否定論理積#完全性を参照)。

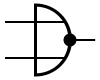

記号

MIL論理記号及びANSI、IEC、DINのそれぞれにおけるNORの記法を以下に示す。

|

|

|

| MIL/ANSI 記号 | IEC 記号 | DIN 記号 |

ハードウェアの解説とピン配置

NORは、汎用ロジックICではNANDに次ぐ基本的な製品として、バリエーション等が最も豊富な一群のひとつである。74シリーズについてはTTLの7402等の他、74HC02他のCMOS版など多数のバリエーションがある。

- 74シリーズ

- 7402: 2入力NORゲート×4

- 7427: 3入力NORゲート×3

- 7425: 4入力NORゲート×2

- 74260: 5入力NORゲート×2

- 744078: 8入力NORゲート×1

- 4000シリーズ(CMOS)

- 4001: 2入力NORゲート×4

- 4025: 3入力NORゲート×3

- 4002: 4入力NORゲート×2

- 4078: 8入力NORゲート×1

さらに古いRTLやECLといった方式ではNORゲートは効率がよかったため多用されていた。

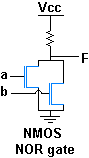

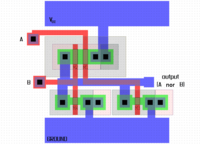

実装

下の左端の図はNMOSで2入力NORゲートを構成した例である。入力のどちらかでもHIGHになれば、対応するMOSFETがONになり、出力をLOWにする。そうでない場合はプルアップ抵抗で出力をHIGHに保っている。下の右端の図はCMOSテクノロジーによる2入力NORゲートの回路図である。入力に付加されているダイオードと抵抗器はCMOS部品を静電放電から守るためのもので、論理的には何の機能もない。

|

|

|

代替実装

NORゲートが入手できない場合、NANDゲートを使って下の図のようにNORゲートを構成できる。NANDゲートやNORゲートは、どちらもそれだけで任意の論理ゲートを構成可能である。

|

|