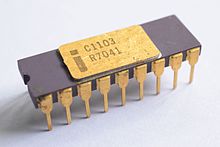

インテル 1103

表示

| Intel 1103 | |

|---|---|

パッケージがセラミックに変更された C1103。 | |

| メディアの種類 | 8 μm p-MOS DRAM |

| 記録容量 | 1 キロビット |

| 国際規格 | 18ピンデュアル・インライン・パッケージ |

| 策定 | Intel |

| 主な用途 | HP 9800 series計算機[1]、PDP-11[2]、MAXC[3]、その他。 |

1103 はインテル社が開発・製造したダイナミック・ランダム・アクセス・メモリ (DRAM) 集積回路 (IC) である。

解説

[編集]1970年10月に発表された1103は、商業的に利用可能な最初のDRAM ICであり、その小さなサイズと磁気コアメモリと比較しての価格の安さにより、多くのアプリケーションで磁気コアメモリに取って代わった[4][5]。

1970年に発表された当初は歩留まりが悪く、1971年に大量に入手できるようになったのは、生産マスクの5段階目になってからであった。

インテルは1974年6月に25万個目の1103 RAMを出荷した[6]。

開発

[編集]1969年、ハネウェルのウィリアム・レジッツと彼の同僚は、3トランジスタのダイナミック・メモリ・セルを発明し、半導体業界に生産者を探し始めた。設立されたばかりのインテル社はこれに応え、ウィリアム・レジッツと密接に協力したジョエル・カープの指揮の下、非常によく似た2つの1024ビットチップ、1102と1103を開発したが[7]、最終的には 1103 のみが生産された。

マイクロシステムズ・インターナショナルは、1971年に1103の最初のセカンドソースとなった[8]。その後、ナショナルセミコンダクター、シグネティクス、シナテックも1103を製造した。

技術詳細

[編集]

| tRWC | 580 ns | ランダム読み出し/書き込みサイクル時間(プリチャージエッジから次のプリチャージエッジまで |

| tPO | 300 ns | アクセス時間: プリチャージHighから有効データ出力まで |

| tREF | 2 ms | リフレッシュレート |

| VCC | 16 V | 供給電圧 |

| p-MOS | 8<span typeof="mw:Entity" id="mwVg"> </span>μm[9] | 製造プロセス(シリコンゲートMOSFET) |

| Capacity | 1024x1 | 容量×バス幅 |

脚注・参考文献

[編集]- ^ Mary Bellis (August 25, 2016). “Who Invented the Intel 1103 DRAM Chip”. ThoughtCo. 2023年12月10日閲覧。

- ^ PDP-11/45, 11/50, and 11/55 System Maintenance Manual. Digital Equipment Corporation. (September 1976)

- ^ Fiala, Edward R. (May 1978). “The Maxc Systems”. GitHub. IEEE Computer Society. October 12, 2022閲覧。 “The most significant contributor to reliability has been main-memory error correction. During the first six months of operation, we replaced about 12 failing 1Kx1 MOS RAMs per month: this has gradually declined to about three failures a month during the last three years. However, because of error correction, a negligible number of these failures has caused crashes.”

- ^ Jacob, Bruce et al. (2008). Memory Systems: Cache, DRAM, Disk. Morgan Kaufmann Publishers. pp. 457–458.

- ^ Jacob, Bruce et al. (2008). Memory Systems: Cache, DRAM, Disk. Morgan Kaufmann Publishers. pp. 457–458.

- ^ A Milestone for the 1103

- ^ Computer History Museum: "Oral History of Joel Karp" Interviewed by Gardner Hendrie March 3, 2003 | Atherton, California

- ^ Tedlow, Richard S. (2006). Andy Grove: The Life and Times of an American. Portfolio. pp. 141–142. ISBN 9781591841395

- ^ Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. pp. 362–363. ISBN 9783540342588. "The i1103 was manufactured on a 6-mask silicon-gate P-MOS process with 8 μm minimum features. The resulting product had a 2,400 μm2 memory cell size, a die size just under 10 mm2, and sold for around $21."