フラッシュADC

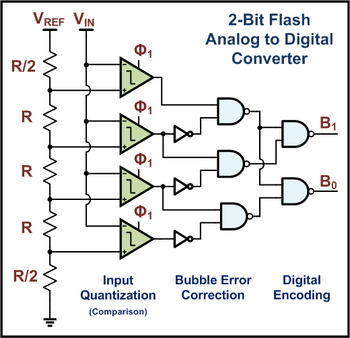

フラッシュADC(フラッシュAD変換器、直接変換ADC)は、入力電圧と連続する基準電圧を比較するために、ラダーの各「ラング(rung)」にコンパレータを取り付けた線形電圧ラダーを用いるアナログ-デジタル変換回路の一種。多くの場合、これらの基準ラダーは多くの抵抗から構成される。しかし近年、容量性の電圧分割で実装することも可能であることが示されている。一般的にこれらのコンパレータの出力はデジタルエンコーダに入力され、デジタルエンコーダは入力をバイナリ値に変換する(コンパレータから集めた出力は一進法の値であると考えられる)。

利点と欠点[編集]

フラッシュ変換器は、他の多くのタイプのADCと比較すると非常に高速である。普通のADCは一連の段階で「正しい」答えが絞り込んでゆくが、フラッシュ変換器は非常に簡単で、アナログ比較器以外ではバイナリへの最終変換のロジックのみが必要である。

最良の精度を得るために、ADCの入力の前にトラックアンドホールド回路が挿入されることがよくある。これは多くのADC(逐次比較型ADCなど)に必要だが、フラッシュADCの場合コンパレータはサンプリングのデバイスであるため、実際は必要がない。

フラッシュ変換器は特に精度が上がるにつれて、他のADCと比較して膨大な数のコンパレータが必要になる。フラッシュ変換器はnビットの変換に個のコンパレータを必要とする。大きさ、消費電力、コストを考えると8ビット(255個のコンパレータ)をはるかに超える精度ではフラッシュ変換器は一般的に実用に耐えうるものではない。これらのコンパレータの代わりに、他のADCのほとんどはより複雑なロジックやアナログ回路に置き換えることで、精度を上げ、より簡単にスケーリングすることができる。

実装[編集]

フラッシュADCは、シリコンベースのバイポーラ(BJT)技術と相補型金属酸化膜FET(CMOS)技術から、めったに使われないIII-V技術に至るまで、多くの技術を用いて実装されている。このタイプのADCは、よく最初の中型アナログ回路の検証として使用される。

最初期に実装されたものは、基準電圧に接続されたよく整合した抵抗の基準ラダーで構成された。抵抗ラダーの各タップは、1つのコンパレータに使用される(このとき増幅段が先行している)。したがって測定した電圧が抵抗タップの基準電圧を上回るか下回るかによって論理0か1が生成される。増幅器を追加する理由は2つの側面がある。電圧差を増幅してコンパレータのオフセットを抑制することと、基準ラダーに対するコンパレータのはね返りを強く抑制することである。普通設計が行われるのは4ビットから6ビット、ときどき7ビットといった感じである。

省電力容量性基準ラダーを用いた設計が実証されている。これらのシステムはコンパレータをクロックすることに加え、入力段の基準値のサンプリングも行う。サンプリングが非常に高速で行われるため、キャパシタの漏れは無視してよいほど小さくなる。

近年では、フラッシュADCの設計にオフセット較正が導入されている。高精度のアナログ回路(ばらつきを抑えるために部品の大きさを大きくする)ではなく、比較的大きなオフセット誤差を持つコンパレータが測定され、調整される。テスト信号が印加され、各コンパレータのオフセットはADCのLSB値より下に較正される。

多くのフラッシュADCのもう1つの改善点は、デジタルエラー訂正機能を組み入れることである。ADCが過酷な環境で使用されたり、非常に小さな集積回路プロセスから構築されていたりすると、単一のコンパレータがランダムに状態を変化させ、誤ったコードを生じるリスクが高まる。バブルエラー訂正は、例えば論理がハイにトリップされたコンパレータが、論理がローだと報告するコンパレータに囲まれている場合、ハイになるうことを防止するデジタル補正の仕組みである。素直には3入力の多数決回路により実現できる。入力がthermometer code(「00000111」のような、連続する0のあとに連続する1のあるコード)であり、0/1の境から高々1桁離れたバブルしか無い場合には、3入力の001または011を検出する回路でthermometerからone-hotへの変換と同時にバブルエラー訂正が行える。

折りたたみADC[編集]

コンパレータの数は、折りたたみの回路を前部に追加することでいくらか減らすことができ、いわゆる折りたたみADC(folding ADC)を作ることができる。ランプ入力信号の間、フラッシュADCのコンパレータを1回だけ使うのではなく、折りたたみADCはコンパレータを複数回使います。もしmビットの折りたたみ回路をnビットのADCで使う場合、実際のコンパレータの数はからギルバートセルやアナログワイヤードOR回路である。

応用[編集]

このタイプのADCの非常に高いサンプルレートにより、レーダー検出、広帯域無線受信機、電子テスト機器、光通信リンクのような高周波の応用(普通、数GHzの範囲内)が可能になる。多くの場合、フラッシュADCは多くのデジタルデコード機能を含む巨大なICに組み込まれている。

また、ΔΣ変調ループ内に小さなフラッシュADC回路があることもある。

フラッシュADCはNANDフラッシュメモリでも使われている。これではセル当たり最大3ビットが8個の電圧レベルとしてフローティングゲートに格納される。

参考[編集]

- Analog-to-Digital Conversion

- Understanding Flash ADCs

- "Integrated Analog-to-Digital and Digital-to-Analog Converters", R. van de Plassche, ADCs, Kluwer Academic Publishers, 1994.

- "A Precise Four-Quadrant Multiplier with Subnanosecond Response", Barrie Gilbert, IEEE Journal of Solid-State Circuits, Vol. 3, No. 4 (1968), pp. 365–373