ビア (電子回路)

ビア(via、ラテン語で「通路」または「道」の意味)とは、2つ以上の金属層間の電気的接続のことで、多層プリント基板(PCB)と三次元集積回路[1]の製造で使用される。

基本的にビアとは、2つ以上の隣接する層を貫通する小さな穴のことである。

プリント基板製造の場合[編集]

プリント基板製造の場合は、穴は金属(多くの場合、銅)でメッキされ、絶縁層を介して電気的接続を形成する。プリント基板(PCB)設計では、ビアは基板の異なる銅層上の対応する位置にある2つのパッドで構成され、基板を貫通する穴によって電気的に接続される。

ビアの重要性[編集]

PCB製造においてビアは重要である[2]。なぜなら、ビアは一定の公差で穴あけされ、指定された位置から外れて製造される可能性があるため、製造前にドリル位置の誤差をある程度許容しておかなければならず、そうでなければ(ある基準規格に従った)不適合基板、あるいは故障基板によって製造歩留まりが低下する可能性があるからである。さらに、通常のスルーホール・ビアは細長いため、壊れやすい構造と考えられている。製造者は、ビアがバレル(ドリルで開けられた穴を埋める導電性チューブ)全体に適切にメッキされていることを確認しなければならず、そのためにいくつかの処理工程が発生する。

穴は電気めっきで導電性にするか、チューブやリベットで裏打ちされる。 高密度多層PCBにはマイクロビアが存在する場合がある。ブラインドビアは基板の片面のみに露出し、埋設ビアはどちらの表面にも露出せずに内部層を接続する。サーマルビアは、パワーデバイスから熱を逃がすもので、通常、約12本のアレイで使用される[3][4]。

ビアは次のもので構成される:

- バレル — ドリルで開けられた穴を埋める導電性チューブ。

- パッド — バレルの各端をコンポーネント、平面、またはトレースに接続する。

- アンチパッド — バレルと金属層の間の、接続されていないクリアランス ホール。

ビアはPTVまたはメッキスルービアと呼ばれることもあるが、メッキスルーホール(PTH)と混同してはならない。ビアはPCB上の銅層間の相互接続として使用されるが、PTHは一般的にビアより大きく作られ、非SMT抵抗、コンデンサ、DIPパッケージICなどの部品リードを受け入れるためのめっき穴として使用される。また、PTHは機械的接続用の穴としても使用できるが、ビアは使用できない。PTHのもう一つの用途は、キャステレーション・ホールとして知られ、PTHはボードの端に配置され、ボードがパネルからフライス加工されるときに半分にカットされる。主な用途は、1つのPCBをスタック内の別のPCBにはんだ付けできるようにすることである[5]。

(1) スルーホール

(2) ブラインド・ビア

(3) 埋設ビア

灰色と緑色の層は非導電性で、オレンジ色の薄い層と赤いビアは導電性である。

右図に示すのは、3種類の主なビアである。PCB製造の基本的な手順は、基板材料を作り、それを層状に積み重ねること、ビアを形成するために穴をあけ貫通させメッキすること、フォトリソグラフィとエッチングを使用して銅トレースをパターン化することである。この標準的な手順では、可能なビア構成はスルーホールに限られる[注釈 1]。レーザーを使用するような深さ制御の穴あけ技術は、より多様なビアタイプを可能にする(レーザードリルは、機械的なドリルよりも小さく、より正確に位置決めされた穴にも使用できる)。PCB製造は通常、いわゆるコアと呼ばれる基本的な両面PCBから始まる。最初の2層以降の層は、この基本構成ブロックから積層される。コアの下からさらに2層を連続して積層すると、1-2ビア、1-3ビア、スルーホールができる。ビアの各タイプは、各積層段階で穴あけ加工によって作られ、1つの層がコアの上に積層され、もう1つの層が下から積層される場合、可能なビア構成は1-3、2-3、およびスルーホールである。ユーザーは、PCBメーカーが許容する積層方法と可能なビアに関する情報を収集しなければならない。安価な基板では、スルーホールのみを作り、ビアと接触しないはずの層にはアンチパッド(またはクリアランス)を配置する。

米国電子回路協会(IPC)のビアに関する規格 IPC 4761[編集]

IPC 4761 では、次のビア タイプが定義されている:

- Type I: Tented via

- Type II: Tented & covered via

- Type III-a: Plugged via, sealed with non-conductive material on one side

- Type III-b: Plugged via, sealed with non-conductive material on both sides

- Type IV-a: Plugged & covered via, sealed with non-conductive material and covered with wet solder mask on one side

- Type IV-b: Plugged & covered via, sealed with non-conductive material and covered with wet solder mask on both sides

- Type V: Filled via, filled with non-conductive paste

- Type VI-a: Filled & covered via, covered with dry film or wet solder mask on one side

- Type VI-b: Filled & covered via, covered with dry film or wet solder mask on both sides

- Type VII: Filled & capped via, filled with non-conductive paste and overplated on both sides

失敗時の動作[編集]

うまく作られていれば、PCB ビアは主に銅メッキと PCB の間の面外方向(Z)の膨張と収縮の差によって故障する。この膨張と収縮の差は、銅メッキに周期的な疲労を引き起こし、最終的にはクラックの伝播と電気的なオープンサーキットを引き起こす。さまざまな設計、材料、環境パラメータがこの劣化速度に影響する[6][7]。IPC は堅牢性を確保するため、故障までの時間を計算するラウンドロビン方式を開発した[8][9]。

集積回路製造の場合[編集]

集積回路(IC)設計において、ビアとは、異なる層間の導電接続を可能にする絶縁酸化膜の小さな開口部のことである。シリコンウェーハまたはダイを完全に貫通する集積回路上のビアは、スルーチップ・ビアまたはスルーシリコン・ビア(through-silicon via、TSV)と呼ばれる[10]。ガラス貫通ビア(through-glass vias、TGV)[11]は、シリコン・パッケージに比べてガラス・パッケージの電気的損失が少ないことから、コーニング・グラス社によって半導体パッケージ向けに研究されてきた[12]。最下層の金属と拡散またはポリを接続するビアは、通常「コンタクト」と呼ばれる。

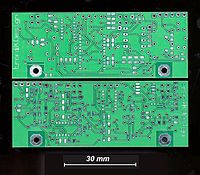

ギャラリー(プリント基板のビア)[編集]

-

メッキスルーホール、この部分には多層基板に8つある(拡大写真)。

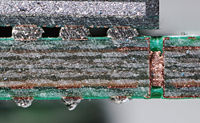

-

メッキスルーホールのメッキ:

上 – 上層

下 – 下層

関連項目[編集]

注釈[編集]

- ^ Through-holes per core. It is possible, though more expensive, to create blind or buried vias by using additional cores and lamination steps. It is also possible to backdrill and remove the plating from one side through to the desired layer, which leaves the physical hole as a through-hole, but creates the electrical equivalent of a blind via. If a PCB needs enough layers to justify blind and buried vias, it is probably also using small enough traces packed tightly enough to require (laser-drilled) microvias.

脚注[編集]

- ^ “三次元LSIとは”. 東北マイクロテック株式会社(T-Micro). 2023年10月22日閲覧。

- ^ “PCB Vias: An In-Depth Guide”. ePiccolo Engineering. 2023年10月22日閲覧。

- ^ “PCB design: A close look at facts and myths about thermal vias”

- ^ Gautam, Deepak; Wager, Dave; Musavi, Fariborz; Edington, Murray; Eberle, Wilson; Dunford, Willa G. (17 March 2013). A review of thermal management in power converters with thermal vias. 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC). Long Beach, California, U.S.A: IEEE. doi:10.1109/APEC.2013.6520276。

- ^ “Castellated Holes / Edge Plating PCB / Castellations”. Hi-Tech Corp. (2011年). 2016年5月26日時点のオリジナルよりアーカイブ。2013年1月2日閲覧。

- ^ C. Hillman, Understanding plated through via failures, Global SMT & Packaging – November 2013, pp 26-28, https://www.dfrsolutions.com/hubfs/Resources/services/Understanding_Plated_Through_Via_Failures.pdf?t=1514473946162

- ^ C. Hillman, Reliable Plated Through Via Design and Fabrication, http://resources.dfrsolutions.com/White-Papers/Reliability/Reliable-Plated-Through-Via-Design-and-Fabrication1.pdf

- ^ “Plated Through Hole (PTH) Fatigue calculator”. DfR Solutions. 2017年12月17日閲覧。

- ^ “Guaranteeing Reliability with Thermal Cycling”. https://thermal.live/. DfR Solutions. 2023年10月22日閲覧。

- ^ “【TSV 半導体】貫通電極”. ヱビナ電化工業株式会社 (2022年1月6日). 2023年10月22日閲覧。

- ^ “TGV(Through-Glass Via、ガラス貫通電極)”. ヱビナ電化工業株式会社 (2022年1月6日). 2023年10月22日閲覧。

- ^ “Progress and Application of Through Glass Via (TGV) Technology”. corning.com. 2019年8月8日閲覧。

参考文献[編集]

- “Tips for PCB Vias Design”. Quick-teck (2014年). 2017年12月18日閲覧。

- “Via Tenting - Overview of the variations”. WE Online. Würth Elektronik GmbH & Co. KG (2014年). 2017年12月18日時点のオリジナルよりアーカイブ。2017年12月18日閲覧。

- “Via Plugging - Overview of the variations”. WE Online. Würth Elektronik GmbH & Co. KG (2014年). 2017年12月18日時点のオリジナルよりアーカイブ。2017年12月18日閲覧。

- “Via Filling - Overview of the variations”. WE Online. Würth Elektronik GmbH & Co. KG (2013年). 2017年12月18日時点のオリジナルよりアーカイブ。2017年12月18日閲覧。

- “Microvia Filling”. WE Online. Würth Elektronik GmbH & Co. KG (2015年). 2017年12月18日時点のオリジナルよりアーカイブ。2017年12月18日閲覧。

- “Pluggen / Plugging” (ドイツ語). FED-Wiki. Berlin, Germany: Fachverband Elektronik-Design e.V. (FED) (2009年3月18日). 2017年12月18日時点のオリジナルよりアーカイブ。2017年12月18日閲覧。

- “Via Optimization Techniques for High-Speed Channel Designs”. Altera Corporation (2008年5月). 2017年12月18日時点のオリジナルよりアーカイブ。2017年12月18日閲覧。

- “Controlled Depth Drilling, or Back Drilling”. Online Documentation for Altium Products. Altium (2017年4月11日). 2017年12月18日時点のオリジナルよりアーカイブ。2017年12月18日閲覧。

- “Removing Unused Pads and Adding Teardrops”. Online Documentation for Altium Products. Altium (2017年5月30日). 2017年12月18日時点のオリジナルよりアーカイブ。2017年12月18日閲覧。

- PCB Trace and Via Temperatures: The Complete Analysis (2nd ed.). CreateSpace Independent Publishing Platform. (2017-02-09). ISBN 978-1541213524

外部リンク[編集]

- PCB Via Calculator The CircuitCalculator.com

- Online Via Calculator (Ampacity, Capacitance, Impedance, Power Dissipation Calculation).