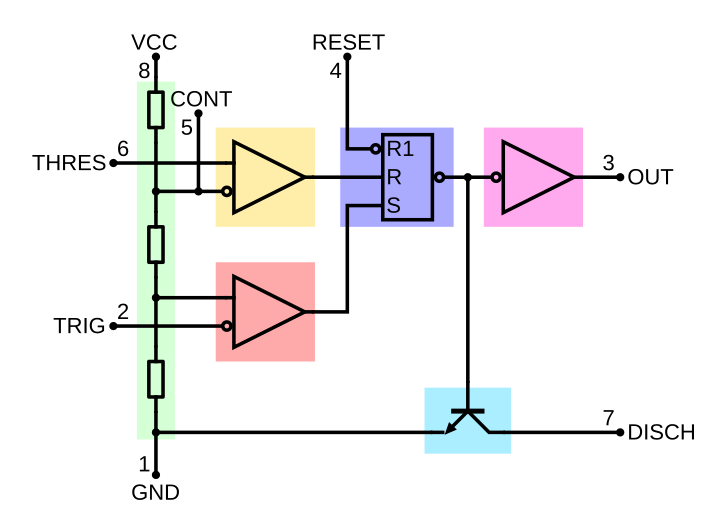

ファイル:NE555 Bloc Diagram.svg

この SVG ファイルのこの PNG プレビューのサイズ: 723 × 524 ピクセル. その他の解像度: 320 × 232 ピクセル | 640 × 464 ピクセル | 1,024 × 742 ピクセル | 1,280 × 928 ピクセル | 2,560 × 1,855 ピクセル。

元のファイル (SVG ファイル、723 × 524 ピクセル、ファイルサイズ: 32キロバイト)

ファイルの履歴

過去の版のファイルを表示するには、その版の日時をクリックしてください。

| 日付と時刻 | サムネイル | 寸法 | 利用者 | コメント | |

|---|---|---|---|---|---|

| 現在の版 | 2012年1月16日 (月) 19:54 |  | 723 × 524 (32キロバイト) | Wdwd | Colored function blocks (for circiut diagram) correct transistor symbol (without a circle, because it's inside the chip) |

| 2009年6月7日 (日) 23:27 |  | 723 × 524 (40キロバイト) | Brighterorange | remove spurious red dot | |

| 2007年9月23日 (日) 20:22 |  | 723 × 524 (40キロバイト) | BlanchardJ | {{Information |Description=Bloc diagram of a 555 timer IC |Source=self-made |Date=September 23 2007 |Author=BlanchardJ |Permission= |other_versions= }} {{Created with Inkscape}} {{ElCompLib}} Category:555 timer IC |

ファイルの使用状況

以下のページがこのファイルを使用しています:

グローバルなファイル使用状況

以下に挙げる他のウィキがこの画像を使っています:

- ar.wikipedia.org での使用状況

- beta.wikiversity.org での使用状況

- ca.wikipedia.org での使用状況

- cs.wikipedia.org での使用状況

- cs.wikibooks.org での使用状況

- de.wikipedia.org での使用状況

- en.wikipedia.org での使用状況

- es.wikipedia.org での使用状況

- et.wikipedia.org での使用状況

- fa.wikipedia.org での使用状況

- fi.wikipedia.org での使用状況

- fr.wikipedia.org での使用状況

- fr.wikiversity.org での使用状況

- he.wikipedia.org での使用状況

- hi.wikipedia.org での使用状況

- hu.wikipedia.org での使用状況

- id.wikipedia.org での使用状況

- it.wikipedia.org での使用状況

- lt.wikipedia.org での使用状況

- no.wikipedia.org での使用状況

- pl.wikipedia.org での使用状況

- pt.wikipedia.org での使用状況

- ru.wikipedia.org での使用状況

- uk.wikipedia.org での使用状況

- vi.wikibooks.org での使用状況

- zh.wikipedia.org での使用状況