Low Pin Count

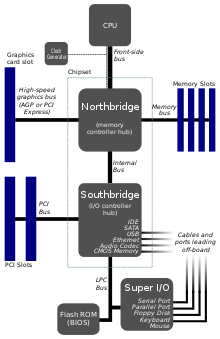

Low Pin Count バス、またはLPCバスは、低帯域幅のデバイス(BIOS ROMやスーパーI/Oチップで接続されるいわゆるレガシーデバイス)をCPUと接続するバスで、IBM互換パーソナルコンピュータで使われている。レガシーデバイスとしては、シリアルポート、パラレルポート、キーボード、マウス、フロッピーディスクコントローラ、さらに最近では Trusted Platform Module などがある。LPCバスは物理的には、PCのマザーボード上でサウスブリッジチップに接続している配線である。

LPCバスは1998年、インテルが Industry Standard Architecture (ISA) バスの代替として提案したバス規格である。この頃インテルはパーソナルコンピュータ向けに、高機能化するCPUや最新インターフェース開発に事業を集中しだしており、なかでもレガシーの代替であるUSBの普及を推進していた。しかしいまだに多くのユーザがレガシーデバイスの利用継続を望んでおり、またこの頃は周辺機器メーカーもUSBの採用には消極的であった。しかしインテルはレガシーインターフェースの利用は過渡的なものと判断し、サウスブリッジからのレガシー削減と過渡的な代替ISAバスの提供を決めた。ソフトウェアから見るとISAとよく似ているが物理的には全く異なり、ISAが8.33MHz動作の16ビットバスだったのに対して、LPCバスは4倍の33.3MHz動作でバスは逆に1/4の4ビット幅である。

LPCの利点は信号線が7本しかない点で、常に混み合っている最近のマザーボードにとっては配置が容易になる。また、LPCインタフェースを採用した集積回路は、ISA対応の同等のチップに比べてピン数が30本乃至72本削減できる。さらに組み込みを容易にするため、PCI バスと同じクロックレートを採用している。なお、LPCはマザーボード上でのみの使用を前提とし、そのためLPC用コネクタ規格が存在しない。

LPC仕様では7本の信号線が必須であり、双方向のデータ転送を行う。うち4本はアドレスとデータを重畳させて運ぶ。残る3本(フレーム、リセット、クロック)は制御信号用であり、特にリセットとクロックはPCIのPCIRST#およびPCICLKと共通化できる。

仕様にはオプションの6本の信号線が定義されていて、割り込み、DMA、スリープ状態からのシステム起動、電源が切れることをLPC機器に知らせるといった用途に使用できる。

LPCのデータ転送レートは、バスアクセスの種類(I/O、メモリ、DMA、ファームウェア)に依存するが、いずれの場合もISAより若干高速である。33.3MHzでの典型的なI/O転送レートは約2.56Mbyte/sである。